计算机组成原理

第一章

第二章

关于非二进制补码编码及其运算

Q:

4位十进制数的模运算系统,模等于[填空1]

该运算系统中,9828+8072= [填空2]

该模运算系统中,-1928表示为什么?

则该模运算系统表示的范围是?

负数的最高为是?正数的最高位是?

A:

10000(1e4)

7900

8072;-5000到4999;

-10000/2到10000/2-1

负数最高位为5,6,7,8,9,整数最高位为0,1,2,3,4

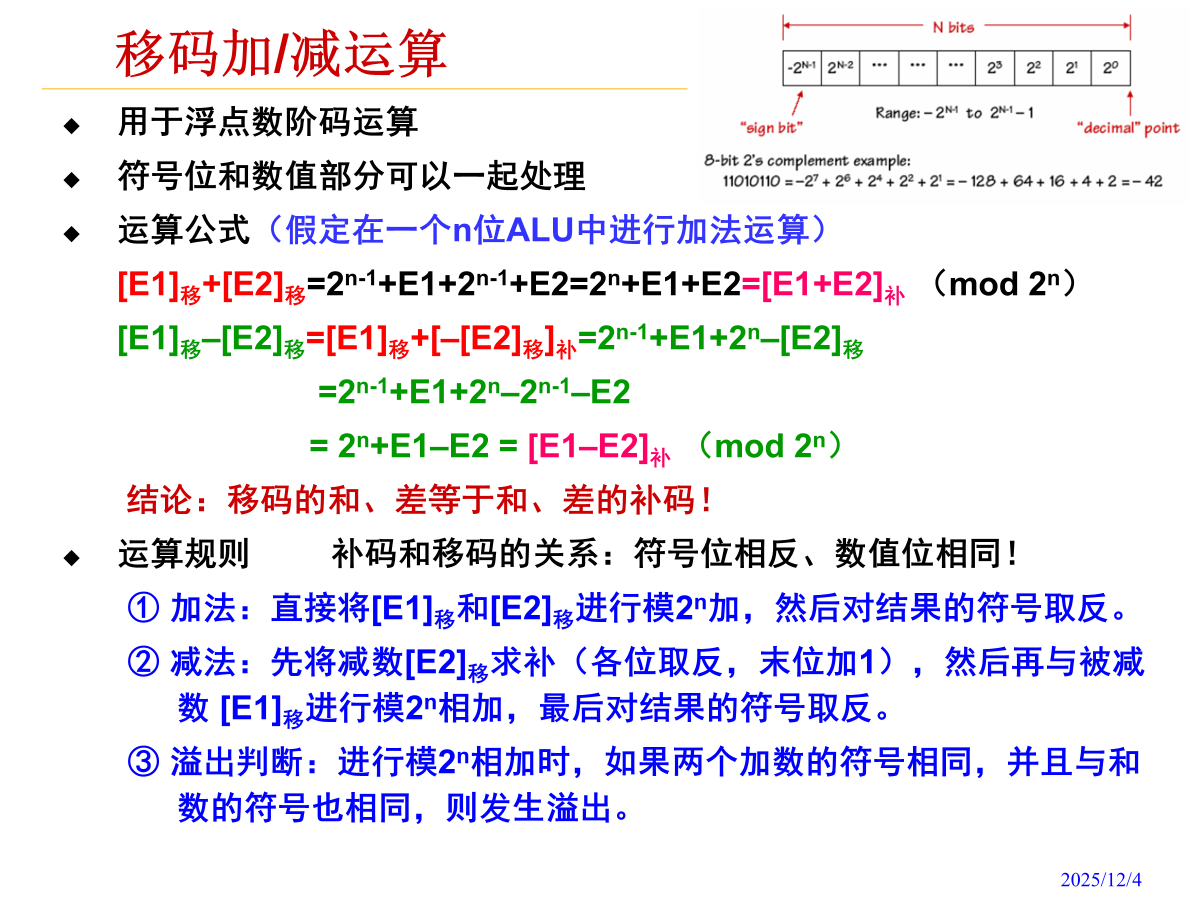

移码

- 移码实际上就是补码+偏移量 记住这一点

大端/小端编码

- 对于0x12345678这串4B的数据可以有大端小端两种模式

-

大端: 高地址 78 56 34 12 低地址 (高位字节排放在内存的低地址端) -

小端: 高地址 12 34 56 78 低地址 - 与大小端相关的还有一个概念,LSB和MSB,最小数位和最大数位,分别对应0x1中的0001的首位0和0x8中1000的末尾0

浮点数

- 特别需要记忆的是32位IEEE标准下的浮点数由1位符号位S,8位阶码E和23位尾数M构成,所以也可以认为是24位的原码,并且阶码偏移量为127

- 表达浮点数范围(考虑隐藏位):

-

正数最大: 0 11111110 11111111111111111111111 - = $ (2-2^{-23})*2^{127} $ (注意若阶码全1则表达无穷)

-

正数规格化最小: 0 00000001 00000000000000000000000 - = $ 1.0*2^{-126} $

- 正数非规格化最小: | 0 | 00000000 | 00000000000000000000001 |

- = $ 2^{-23}*2^{-126} $ (非规格化下阶码无论是多少指数均为-126)

-

- 对于常规浮点数(不考虑隐藏位,规格化定义为最高位为1)

-

正数最大: 0 11111111 11111111111111111111111 - = $ (1-2^{-24})*2^{127} $

-

正数规格化最小: 0 00000000 10000000000000000000000 - = $ 2^{-1}*2^{-128} $

-

第三章

标志位

- 标志位的计算(其中C指进位,F指结果)

- 溢出标志OF: $ OF=C_n \oplus C_{n-1} $

- 符号标志SF:

- $ SF= F_{n-1} $

- 零标志ZF=1当且仅当F=0;

- 进位/借位标志CF: $ CF=C_{out} \oplus C_{in} $

- 根据标志位判断溢出

- 无符号加溢出条件:CF=1

- 带符号加溢出条件:OF=1

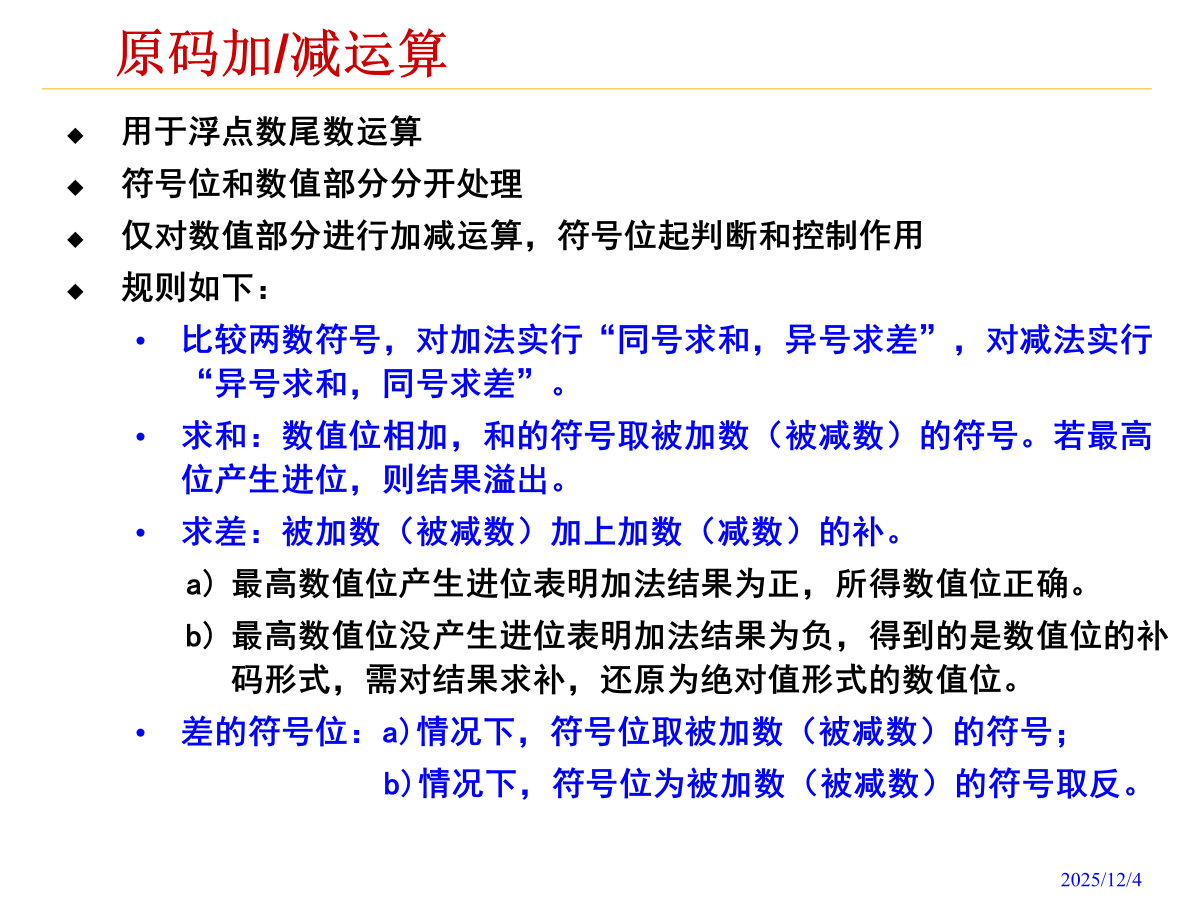

各编码加减运算

- 原码:

- 补码:

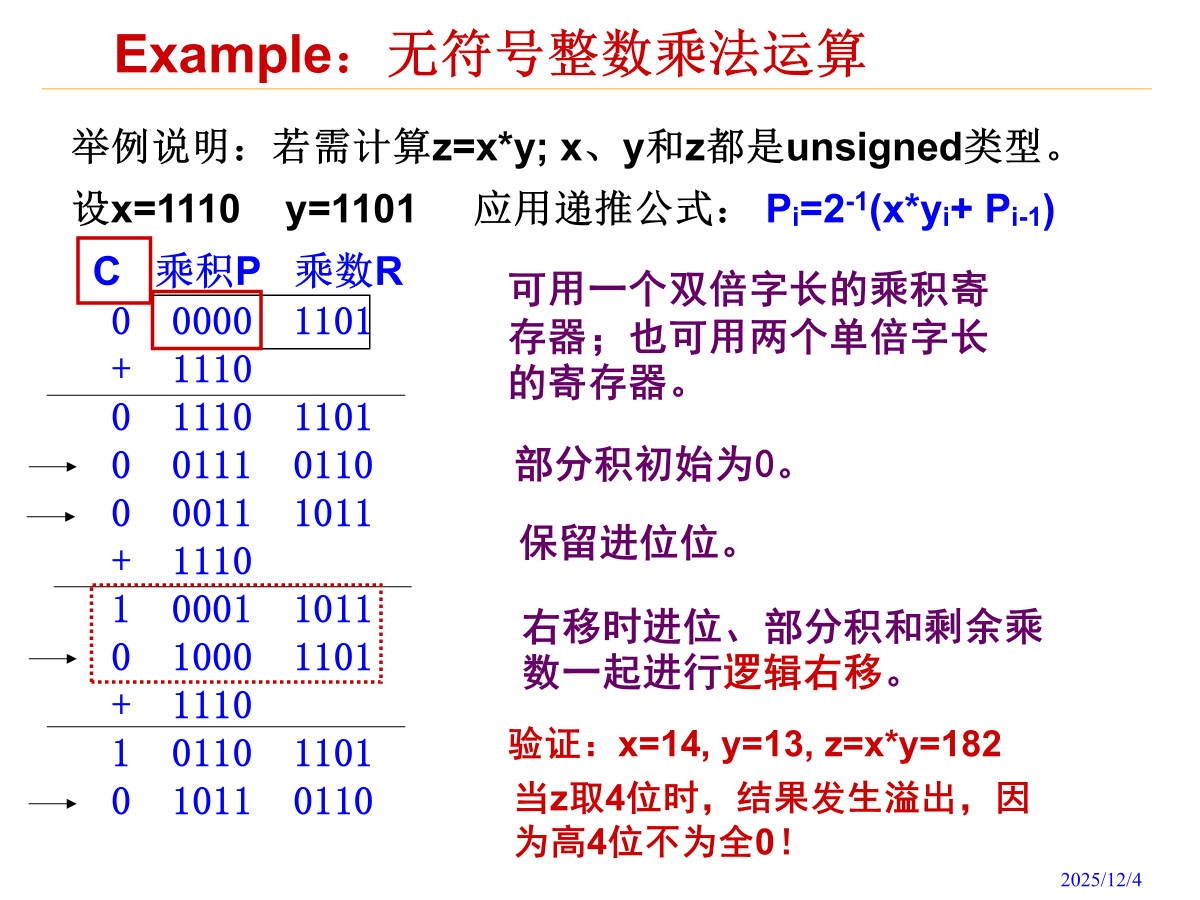

乘法

- 无符号整数乘法运算:

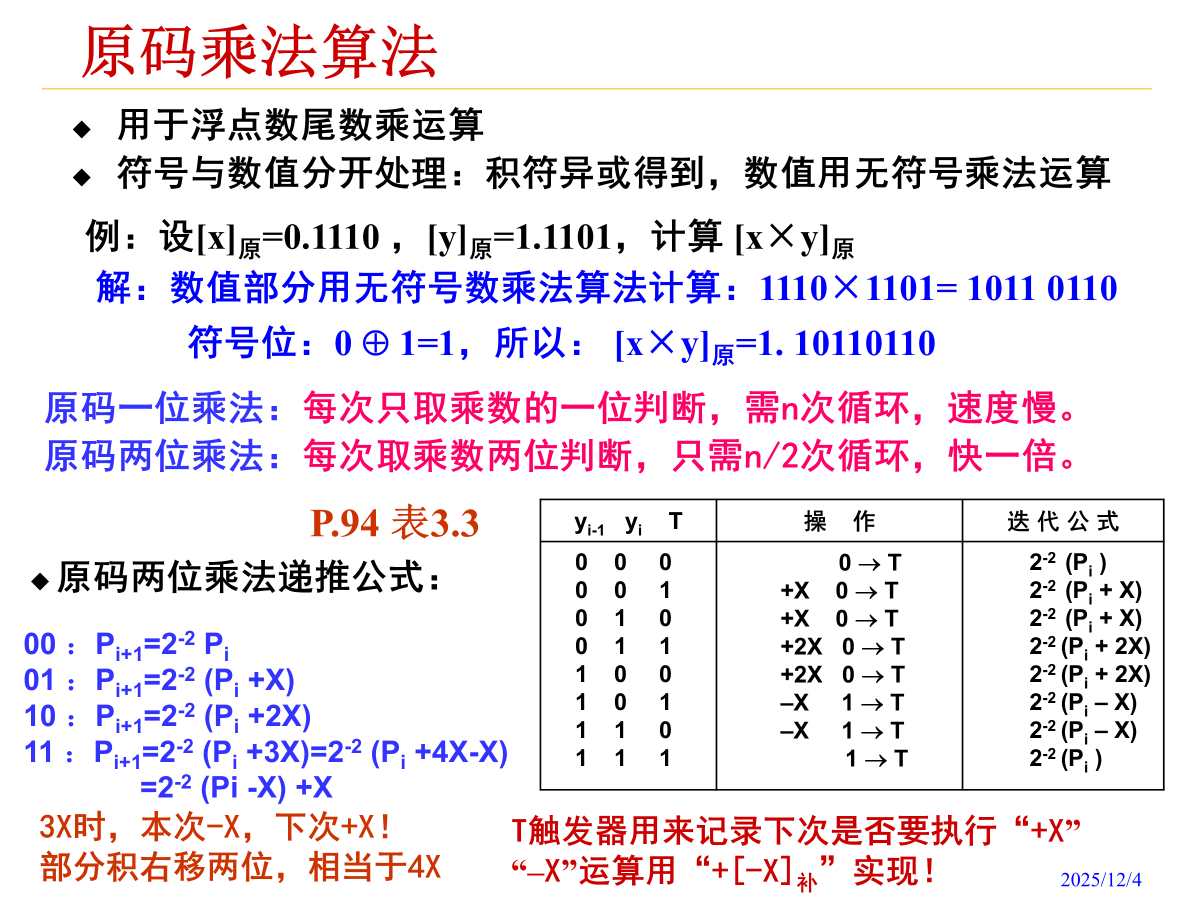

原码乘法算法(包括二位布斯):

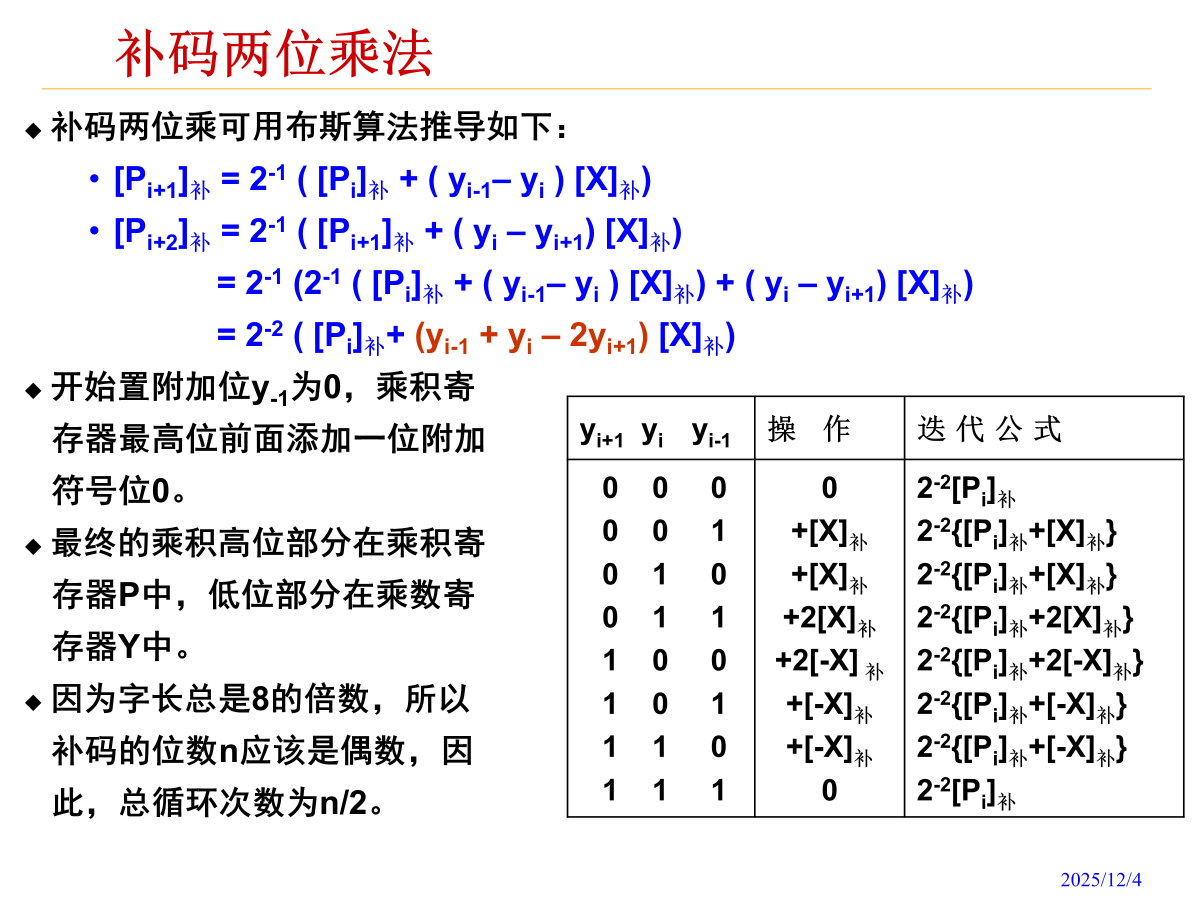

补码乘法运算

- 除法(大概率不考)

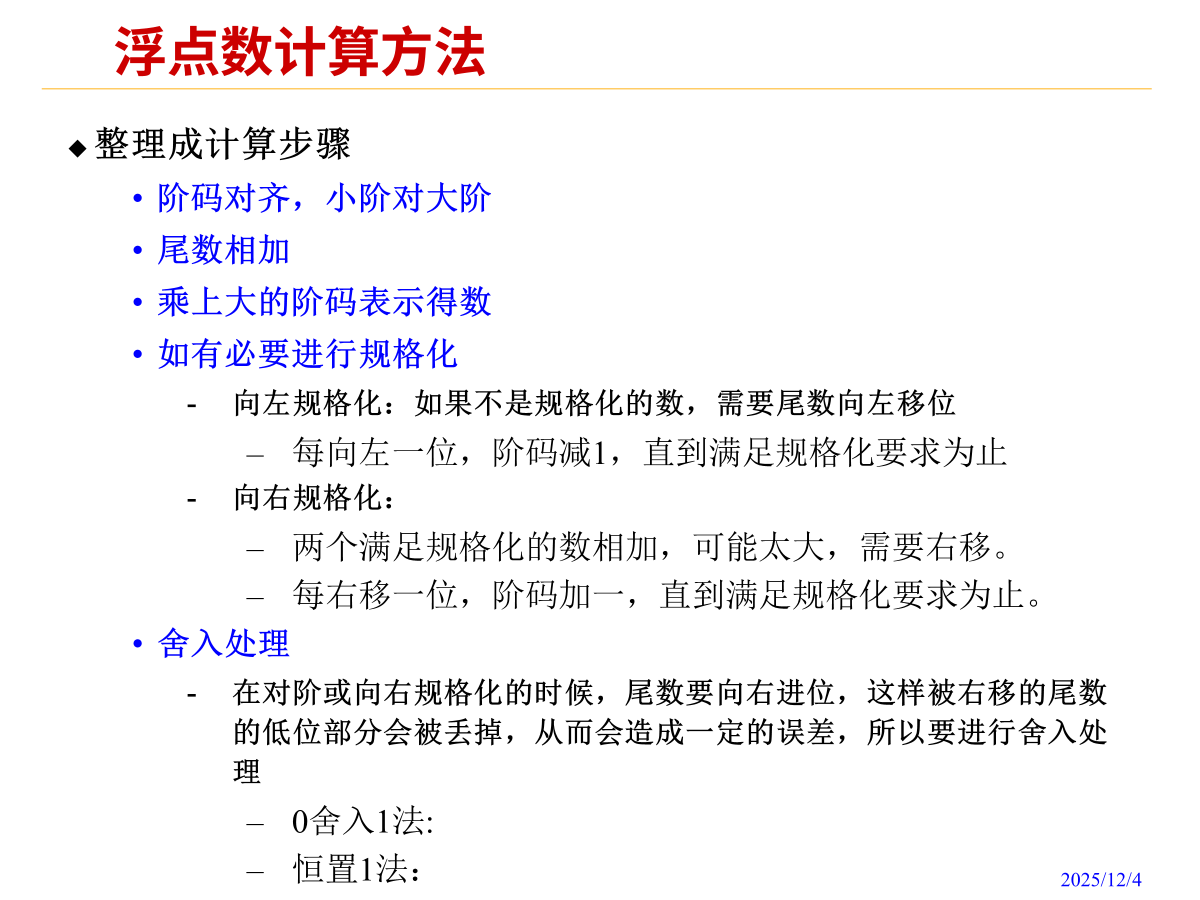

浮点数运算

- 运算规则

第四章

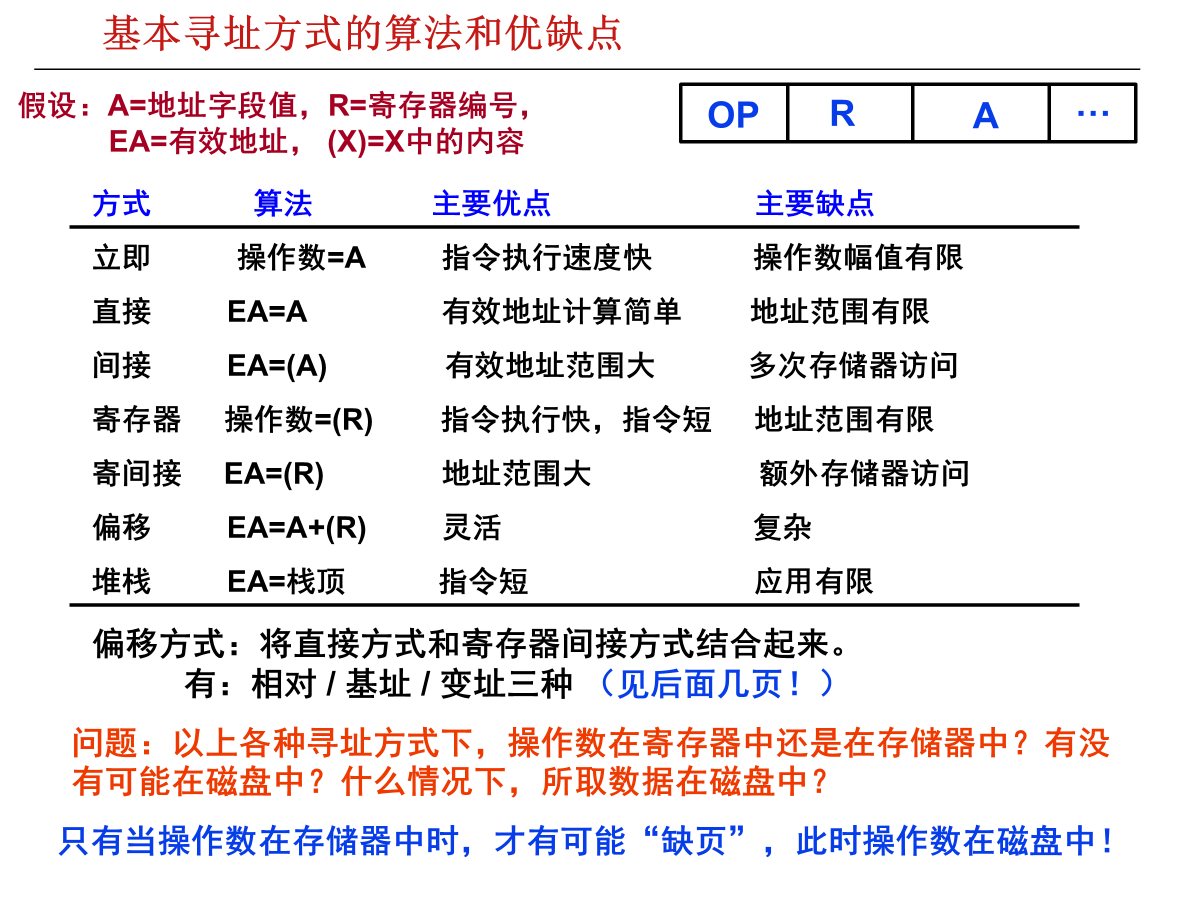

- 基本寻址方式的算法和优缺点:

-

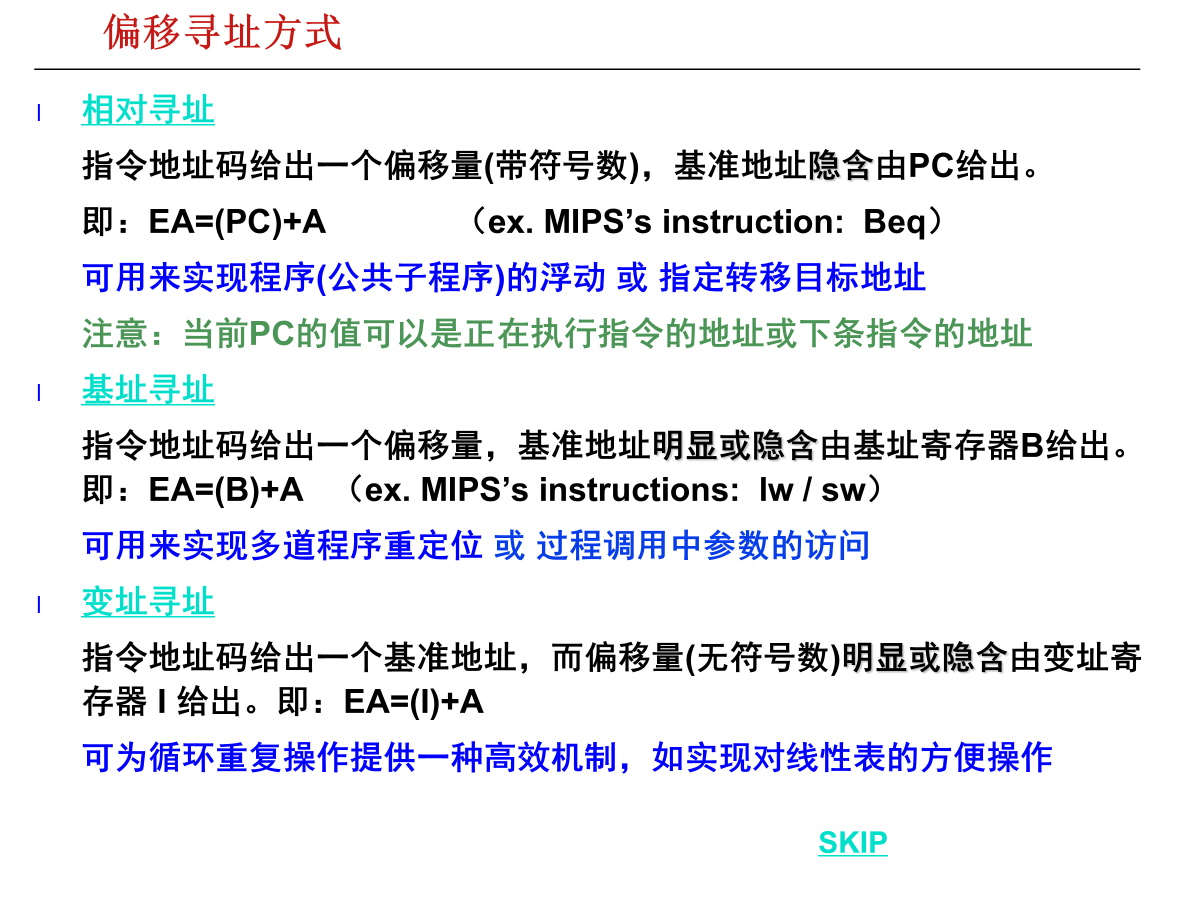

三种偏移寻址方式:

- 一些莫名其妙的考点:

- 什么是数据通路(DataPath)?

- 指令执行过程中,数据所经过的路径,包括路径中的部件。它是指令的执行部件。

- 控制器(Control)的功能是什么?

- 对指令进行译码,生成指令对应的控制信号,控制数据通路的动作。能对执行部件发出控制信号,是指令的控制部件。

- 数据通路如何构成?

- 由“操作元件”和“存储元件”通过总线方式或分散方式连接而成

- 数据通路由两类元件组成

- 组合逻辑元件(也称操作元件)

- 时序逻辑元件(也称状态元件,存储元件)

- 数据通路的功能是什么?

- 进行数据存储、处理、传送

- 区分组合逻辑单元和时序逻辑单元

- 周期时间与时序参数关系 (p131这个我建议还是康康书)

- 同步系统(Synchronous system)

- 所有动作有专门时序信号来定时

- 由时序信号规定何时发出什么动作

- 例如,指令执行过程每一步都有控制信号控制,由定时信号确定控制信号何时发出、作用时间多长

- 什么是时序信号?

- 同步系统中用于进行同步控制的定时信号,如时钟信号

- 什么叫指令周期?

- 取并执行一条指令的时间

- 早期计算机的三级时序系统

- 机器周期 - 节拍 - 脉冲

- 指令周期可分为取指令、读操作数、执行并写结果等多个基本工作周期,称为机器周期。

- 机器周期有取指令、存储器读、存储器写、中断响应等不同类型

- 元件间的连接方式有:

- 总线连接方式

- 分散连接方式

- 什么是数据通路(DataPath)?

第六章

- 记背考点

- 流水线

- 均衡时指令吞吐率提高N倍,但不能缩短一条指令的执行时间

- 流水段数以最复杂指令所需步骤数为准(有些指令的某些阶段为空操作),每个阶段的宽度以最复杂阶段所需时间为准(尽量调整使各阶段均衡)

- 数据冒险的解决方法

- 方法1:硬件阻塞(stall)

- 方法2:软件插入“NOP”指令

- 方法3:合理实现寄存器组的读/写操作

- 方法4:转发(Forwarding或Bypassing 旁路)技术

- 方法5:编译优化–调整指令顺序(不能解决所有数据冒险)

- 控制冒险的解决方法

- 方法1:硬件上阻塞(stall)分支指令后三条指令的执行

- 方法2:软件上插入三条“NOP”指令

- 方法3:分支预测(Predict)。

- 方法4:延迟分支(Delayed branch)(通过编译程序优化指令顺序!)

- 流水线的基本类型

- 按数据的处理形态

- 标量流水线

- 向量流水线

- 按流水线各段的连接模式

- 线性流水线(前馈型)

- 非线性流水线(存在反馈连接)

- 按流水线输入输出对应关系

- 顺序流水线(先进先出)

- 乱序流水线(无序、异步)

- 按数据的处理形态

- 两种指令级并行(ILP)技术(即:高性能流水线形式)

- 超流水线:更多的流水线级数

- 多发射流水线:同时发射多个指令,有多条流水线同时进行

- 静态多发射(VLIW处理器+编译器静态调度)

- 动态多发射(超标量处理器+动态流水线调度)

- 流水线

第七章

- 一些记忆点:

- 硬连线路设计的特点:

- 优点:速度快,适合于简单或规整的指令系统,例如,MIPS指令集。

- 缺点:它是一个多输入/多输出的巨大逻辑网络。对于复杂指令系统来说,结构庞杂,实现困难;修改、维护不易;灵活性差。甚至无法用有限状态机描述!

- 微程序控制器的基本思想:

- 仿照程序设计的方法,编制每个指令对应的微程序

- 每个微程序由若干条微指令构成,各微指令包含若干条微命令 (一条微指令相当于一个状态,一个微命令就是状态中的控制信号)

- 所有指令对应的微程序放在只读存储器中,执行某条指令时,取出对应微程序中的各条微指令,对微指令译码产生对应的微命令,这个微命令就是控制信号。这个只读存储器称为控制存储器(Control Storage),简称控存CS 。

- 微程序设计的特点:

- 具有规整性、可维性和灵活性,但速度慢。

存储器分类- 按工作性质/存取方式分类

- 随机存取存储器 Random Access Memory (RAM) 每个单元读写时间一样,且与各单元所在位置无关。如:内存。 (注:原意主要强调地址译码时间相同。现在的DRAM芯片采用行缓冲,因而可能因为位置不同而使访问时间有所差别。)

- 顺序存取存储器 Sequential Access Memory (SAM) 数据按顺序从存储载体的始端读出或写入,因而存取时间的长短与信息所在位置有关。例如:磁带。

- 直接存取存储器 Direct Access Memory(DAM) 直接定位到读写数据块,在读写数据块时按顺序进行。如磁盘。

- 相联存储器 Associate Memory(AM) Content Addressed Memory (CAM) 按内容检索到存储位置进行读写。例如:快表。

- 按存储介质分类

- 半导体存储器:双极型,静态MOS型,动态MOS型

- 磁表面存储器:磁盘(Disk)、磁带 (Tape)

- 光存储器:CD,CD-ROM,DVD

- 按信息的可更改性分类

- 读写存储器(Read / Write Memory):可读可写

- 只读存储器(Read Only Memory):只能读不能写

- 按断电后信息的可保存性分类

- 非易失(不挥发)性存储器(Nonvolatile Memory) 信息可一直保留, 不需电源维持。 (如 :ROM、磁表面存储器、光存储器等)

- 易失(挥发)性存储器(Volatile Memory) 电源关闭时信息自动丢失。(如:RAM、Cache等)

- 按工作性质/存取方式分类

- 按功能/容量/速度/所在位置分类

- 寄存器(Register) 封装在CPU内,用于存放当前正在执行的指令和使用的数据 用触发器实现,速度快,容量小(几~几十个)

- 高速缓存(Cache) 位于CPU内部或附近,用来存放当前要执行的局部程序段和数据 用SRAM实现,速度可与CPU匹配,容量小(几MB)

- 内存储器MM(主存储器Main (Primary) Memory) 位于CPU之外,用来存放已被启动的程序及所用的数据 用DRAM实现,速度较快,容量较大(几GB)

- 外存储器AM (辅助存储器Auxiliary / Secondary Storage) 位于主机之外,用来存放暂不运行的程序、数据或存档文件 用磁表面或光存储器实现,容量大而速度慢

- 容量扩展方式:

- 交叉编址和连续编址

- 刷新周期:

- 从上次对整个存储器刷新结束到下次对整个存储器全部 刷新一遍为止的时间间隔,也就是相邻两次对某个特定行进行刷新 的时间间隔。 为电容数据有效保存期的上限10ms~100ms,目前公认是64ms。

- 多采用异步刷新方式: 将一个刷新周期分配给所有行,使得在一个刷新周期内每行至少 刷新一次,且仅刷新一次。

- 例如: 以4096行为例,在64ms时间内必须轮流对每一行刷新一次,即 每隔64ms/4096=15.625μs刷新一行

- 刷新周期的安排方式

- 集中刷新

- 分散刷新

- 异步刷新(大多情况)

- CPU和主存之间有同步和异步两种通信方式

- 异步方式(读操作)过程(需握手信号)

- CPU送地址到地址线,主存进行地址译码

- CPU发读命令,然后等待存储器发回“完成”信号

- 主存收到读命令后开始读数,完成后发“完成”信号给CPU

- CPU接收到“完成”信号,从数据线取数

- 写操作过程类似

- 同步方式的特点

- CPU和主存由统一时钟信号控制,无需应答信号(如“完成”)

- 主存总是在确定的时间内准备好数据

- CPU送出地址和读命令后,总是在确定的时间取数据

- 存储器芯片必须支持同步方式

- 异步方式(读操作)过程(需握手信号)

写策略(解决cache一致性问题)- 对于写命中,有两种处理方式

- Write Through (通过式写、写直达、直写)

- 同时写Cache和主存单元

- 使用写缓冲(Write Buffer)

- Write Back (一次性写、写回、回写)

- 只写cache不写主存,缺失时一次写回,每行有个修改位(“dirty bit-脏位”),大大降低主存带宽需求,控制可能很复杂

- Write Through (通过式写、写直达、直写)

- 对于写不命中,有两种处理方式

- Write Allocate (写分配)

- 将主存块装入Cache,然后更新相应单元

- 试图利用空间局部性,但每次都要从主存读一个块

- Not Write Allocate (非写分配)

- 直接写主存单元,不把主存块装入到Cache

- Write Allocate (写分配)

- 对于写命中,有两种处理方式

- 硬连线路设计的特点:

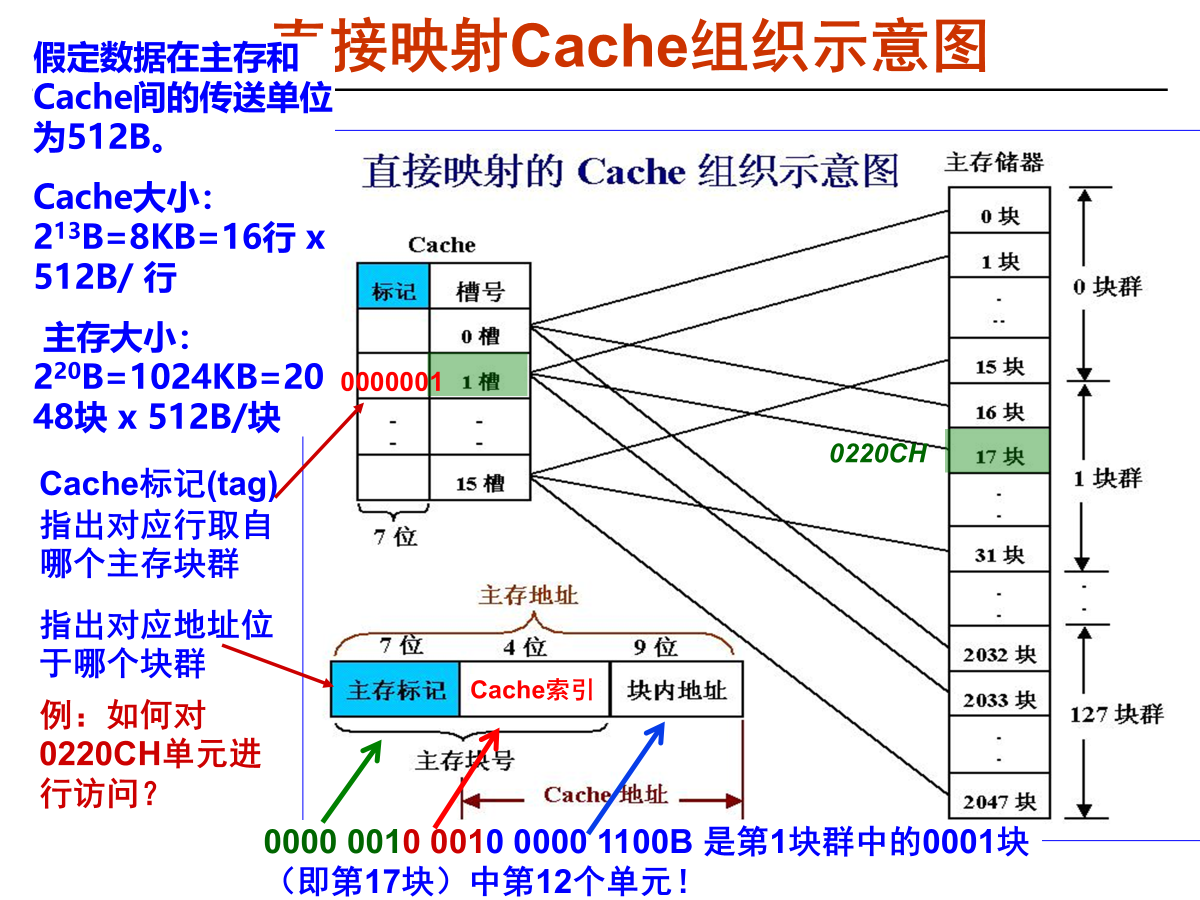

- 直接相联cache组织结构

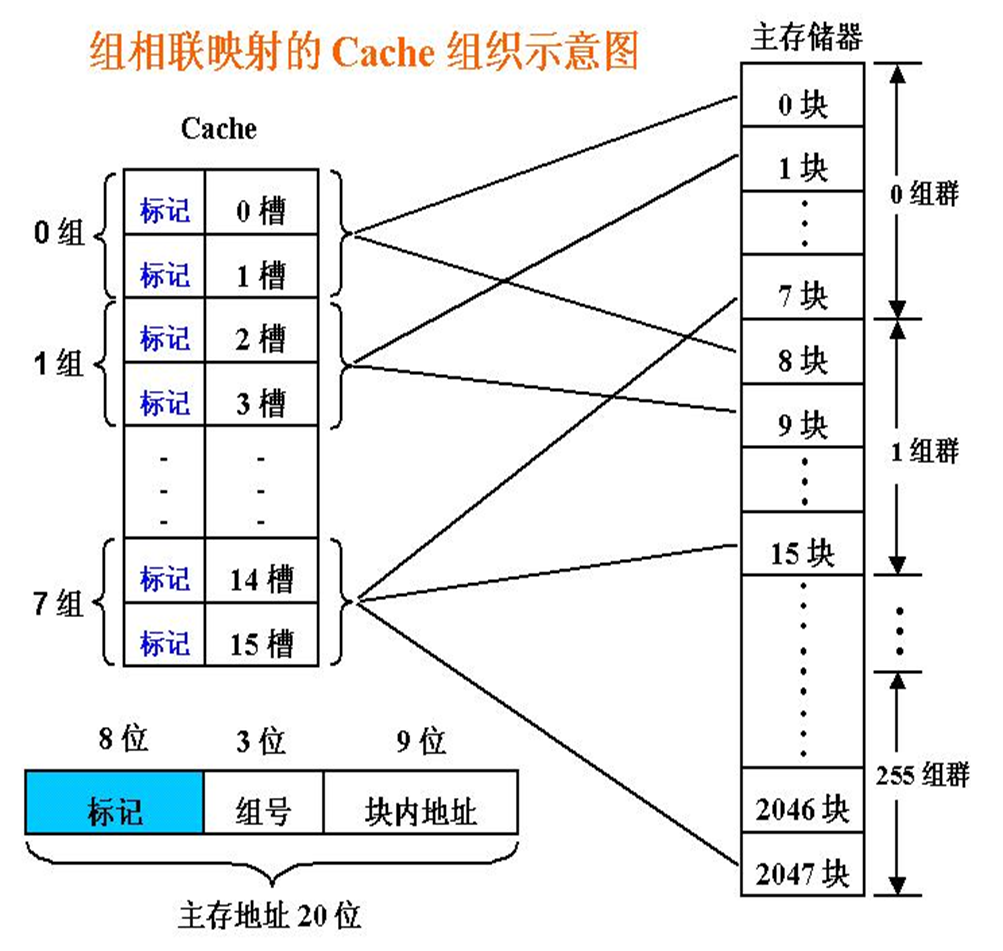

- 组相联cache组织结构

第八章

- 一些记忆点:

- 总线的分类:

- 芯片内总线:

- 在芯片内部各元件之间提供连接

- 系统总线:在系统主要功能部件(CPU 、MM和各种I/O控制器)间提供连接

- 单总线结构

- 将CPU、MM和各种I/O适配卡通过底板总线(Backplane Bus)互连,底板总线为标准总线(Industry standard)

- 多总线结构

- 将CPU、Cache、MM和各种I/O适配卡用局部总线、处理器-主存总线、高速I/O总线、扩充I/O总线等互连。主要有两大类:

- Processor- Memory Bus (Design specific or proprietary)

- 短而快,仅需与内存匹配,使CPU-MM之间达最大带宽

- I/O Bus (Industry standard)

- 长而慢,需适应多种设备,一侧连接到Processor- Memory Bus 或 Backplane Bus,另一侧连到I/O控制器

- 单总线结构

- 通信总线:在主机和I/O设备之间或计算机系统之间提供连接

- 通常是电缆式总线,如SCSI、RS-232、USB、PS-2等

- 芯片内总线:

- 总线裁决(早期计算机)

- 总线定时

- 定义总线事务中的每一步何时开始、何时结束。

- Synchronous (同步):用时钟信号来确定每个步骤

- Asynchronous(异步):用握手信号来定时,前一个信号结束就是下一个信号的开始

- 半同步:结合使用时钟信号和握手信号来定时

- 并行/串行传输

- 并行传输:一个方向同时传输多位数据信号,故位与位需同步,慢!

- 串行传输:一个方向只传输一位数据信号,无需在位之间同步,快!

- 总线的性能指标

- 总线宽度

- 总线带宽

- 总线传送方式

- I/O设备的寻址方式

- 统一编址方式(内存映射方式)

- 与主存空间统一编址,将主存空间分出一部分地址给I/O端口进行编号。 (该方法是将I/O端口映射到某主存区域,故也称为“存储器映射方式”) 例如,RISC机器、Motorola公司的处理器等采用该方案

- 独立编址方式(特殊I/O指令方式)

- 不和主存单元一起编号,而是单独编号,使成为一个独立的I/O地址空间 (因需专门I/O指令,故也称为“特殊I/O指令方式”) 例如,Intel公司和Zilog公司的处理器就是独立编址方式

- 统一编址方式(内存映射方式)

- I/O设备与主机进行数据交换的三种基本方式

- 程序直接控制方式(最简单的I/O方式)

- I/O Interrupt (中断I/O方式): 几乎所有系统都支持的中断I/O方式

- Direct Memory Access (DMA方式): 磁盘等高速外设特有的I/O方式

- 中断源的识别方法

- 软件方法(轮询)

- 硬件方法(向量中断)

- CPU与I/O之间传递信息常采用三种联络方式

- 直接控制(立即响应)、同步、异步

DMA数据传输方式- CPU停止法(成组传送) DMA传输时,CPU脱离总线,停止访问主存,直到DMA传送一块数据结束。

- 周期挪用(窃取)法(单字传送) DMA传输时,CPU让出一个总线事务周期,由DMA控制总线来访问主存,传送完一个数据后立即释放总线。

- 交替分时访问法 每个存储周期分成两个时间片,一个给CPU,一个给DMA,这样在每个存储周期内,CPU和DMA都可访问存储器。

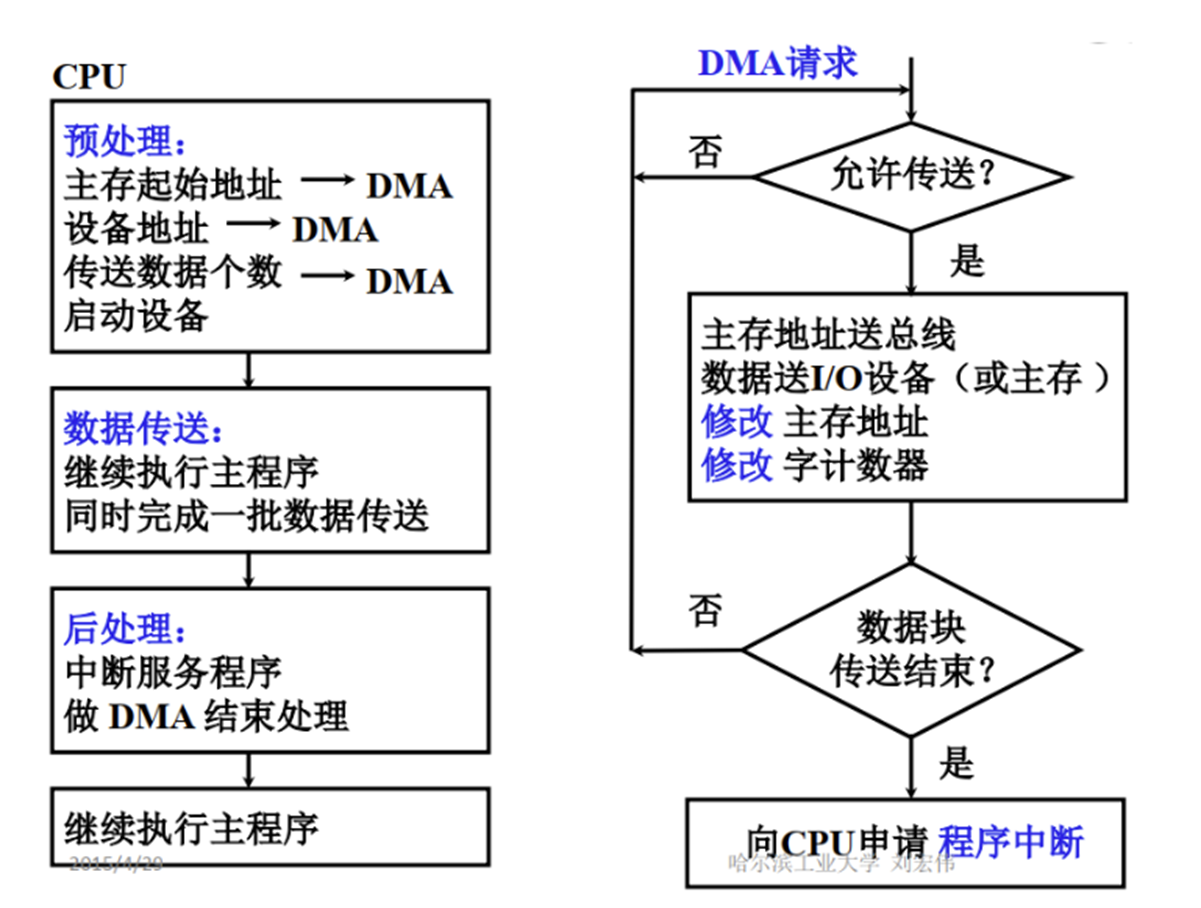

DMA操作步骤- DMA控制器的预置(初始化)—-软件实现

- 准备内存

- 设置参数

- 启动外设

- DMA数据传送—-硬件实现

- DMA请求:选通-〉DMA请求-〉总线请求

- DMA响应:总线响应(CPU让出总线)-〉DMA响应

- DMA传送:DMA控制总线进行数据传送

- DMA结束处理—-软件实现

- 根据计数值为“0”,发出DMA结束信号去接口控制产生 DMA中断请求信号,转入中断服务程序,做一些数据校 验等后处理工作。

- DMA控制器的预置(初始化)—-软件实现

- 总线的分类:

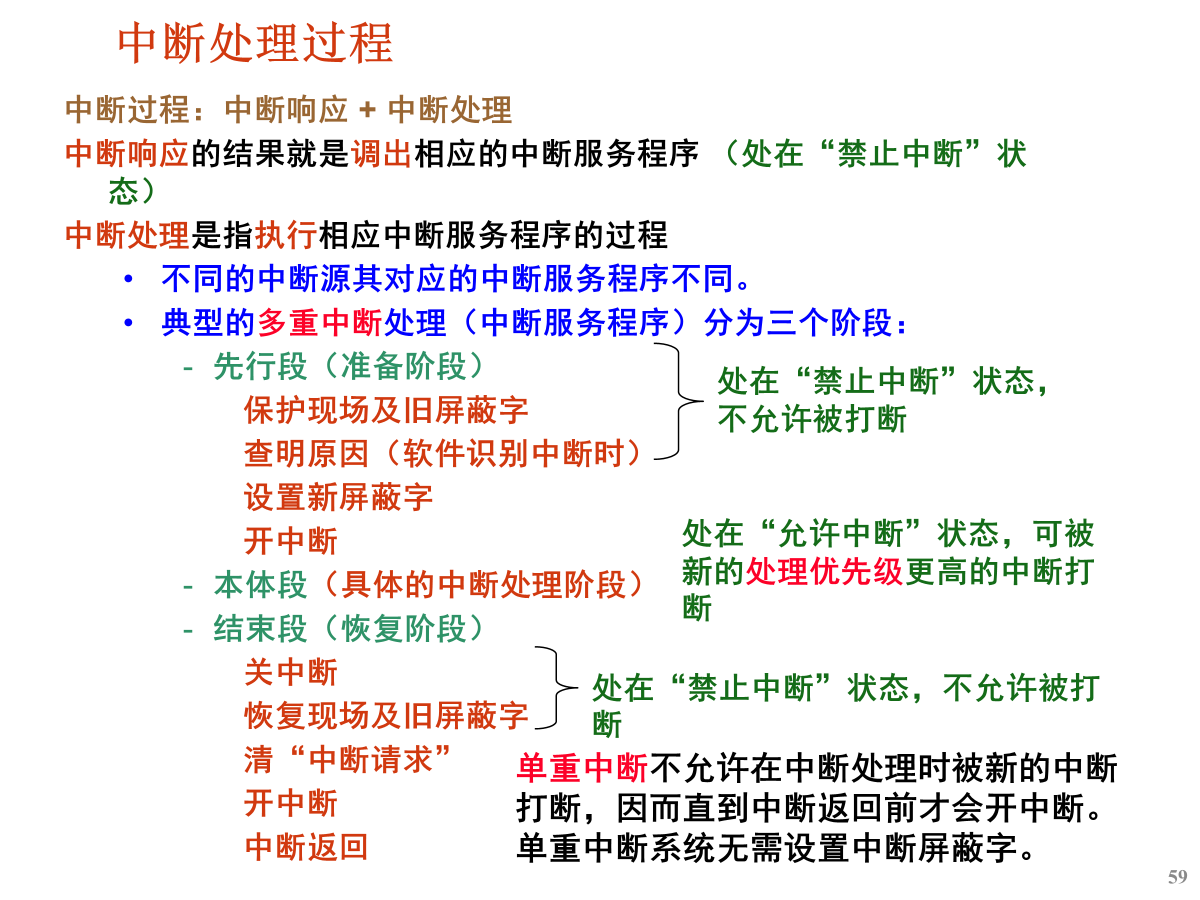

- 中断处理过程

- DMA传输过程